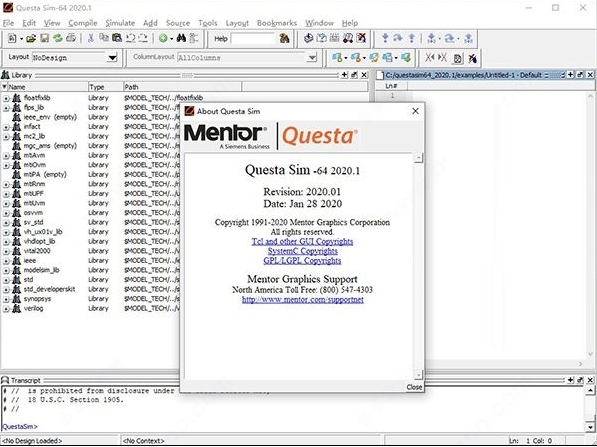

QuestaSim2020是一款仿真模拟软件,用于HDL语言的仿真功能,软件中提供了非常完善的调试环境,包括GUI模式,命令行模式和批处理模式等等,你需要的这里都有,让用户在软件中轻松的进行工作,是语言仿真必备的一款软件。

软件介绍

questasim2020在业界中是一款备受好评及喜爱的HDL语言仿真器,提供了十分友好的调试环境,不仅是唯一的单核支持VHDL和Verilog混合仿真的仿真器,也是电子设计自动化(EDA)的技术领导者,提供了全面的软件和硬件设计解决方案,从而可以使公司更快,更好地开发更优质的电子产品。同时,该软件可是功能强大的仿真工具,支持System C,Verillog,SystemVerilog以及VHDL等硬件描述语言,并questasim2020是Modelsim的加强版,不仅适用于最复杂的回归套件的高性能多语言引擎,还能自由灵活的创建工作和资源库、编译设计、优化设计、加载设计以进行仿真、模拟设计以及进行调试设计等各种流行的操作,并支持多种常规操作模式,包括GUI模式,命令行模式和批处理模式,从而更加好的满足用户的使用需求。

另外,mentor graphics questasim2020.1这个版本是mentor公司全新推出的一个版本,与上个版本相比该软件可是进行了许多的新升级和优化,例如改进了SystemVerilog性能、增强了VHDL性能默认设置、覆盖率数据库、升级了SystemC 2.3.2支持和默认设置、可视化工具调试高性能和大容量(VIS)等等,并所有的更新都只是为了可以给用户们更好的使用体验感,从而即可拥有更高效工作效率,快速的制作出优质的电子产品。

软件特色

1、将高性能和容量仿真与高级调试和功能覆盖功能相结合,为Verilog,VHDL,SystemC和UPF等提供全面的本机支持。

2、通过非常积极的全球编译以及VHDL和SystemVerilog的仿真优化算法,实现了行业和容量的领先性能。

3、提供全面的,基于标准的ABV解决方案,从而提供SystemVerilog和属性规范语言的选择。

4、获得了Questa验证库(QVL),这是一个完整的SystemVerilog断言检查器和监视库,可以很容易地采用ABV。

5、配备高性能,多语言引擎,适用于大多数复杂的回归套件。

6、与Veloce平台进行高带宽事务级集成,以实现显着的模拟加速。

7、通过使用UPF获得Power Aware Simulation的原生支持。

软件功能

1、适用于最复杂的回归套件的高性能多语言引擎

2、高效的高级验证解决方案,具有验证管理功能,可覆盖大型复杂电子系统的覆盖范围

3、通过本机断言和完整的多抽象和多语言调试环境(包括事务级调试),易于使用,快速调试

4、约束随机刺激生成以自动化测试开发

5、具有OVM和UVM的本机高级SystemVerilog测试平台功能与独特的调试功能相结合,可简化高级测试平台的开发和调试

6、高带宽事务级(TBX)与Veloce平台的集成,可实现显着的仿真加速

7、使用UPF对Power Aware Simulation进行原生支持

8、多核仿真,支持所有设计语言和构造,并自动或手动分区设计以并行运行,同时维护单个数据库以进行调试和覆盖

安装教程

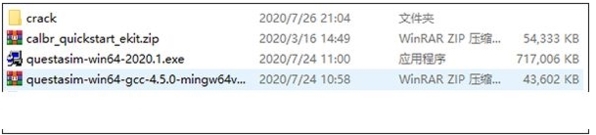

1、先在本页面下载压缩包并解压,得到mentor graphics questasim2020.1。

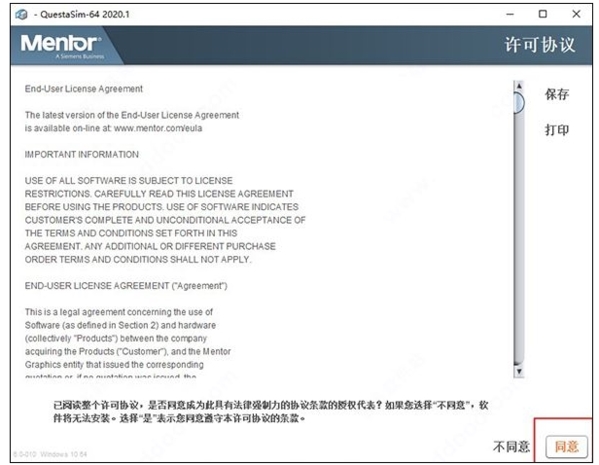

2、我们双击开始软件的安装,选择我们要安装的软件目录

3、选择同意条款,然后等待安装完成;

4、接下来我们继续同意,进行Key Driver的安装;然后我们的额软件就安装完成了。

仿真教程

每次完成代码的编辑之后,下一步就是进行仿真,检查代码中是否有什么问题,可以及时的发现问题并进行解决,那么怎么用软件去进行仿真呢?下面小编为大家带来攻略,介绍仿真的全流程。

1、准备好HDL和testbench文件。

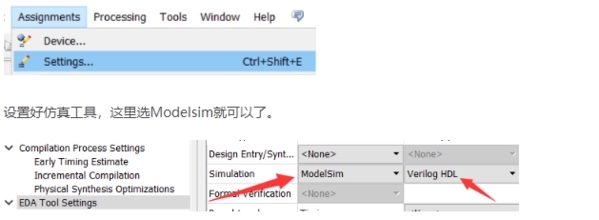

因为QuestaSim不支持原理图输入方式,所以,如果你的工程有原理图的话,一定要先转成HDL(在本博客的《彻底掌握Quartus》有介绍)。

然后,在Assignments->Settings。

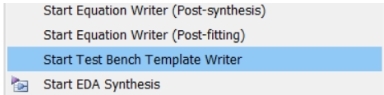

在Processing->Start->开始生成testbench模板。

在工程目录下,simulation\modelsim文件夹里,可以找到这个tb文件。

再把HDL文件和tb文件都拷贝在一个文件夹里面,如下图所示。

2、仿真。

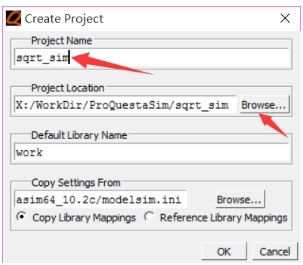

新建工程。

填好工程名和工程目录。

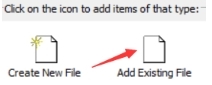

添加已存在的文件(就刚才准备好的HDL文件和tb文件)。

这里Reference from current location是引用文件路径,而Copy to project directory是拷贝到工程目录,这里选择引用就可以了,因为上一步已经拷贝好了。

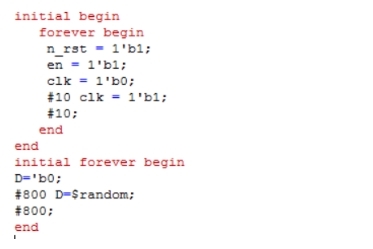

修改一下自动生成的testbench模板,让它能产生正确的激励。

如果HDL文件里面,用到reg型变量,就必须全部对它们赋初值。当然,这个初值是仿真时用的,不影响综合出来的电路。

随便右击一个文件,点击编译全部。

成功的话,会出现如下字样。如有错误,就要改到正确为止。

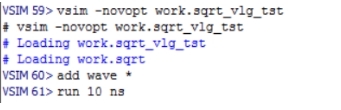

接下来,依次输入三条指令,如下图所示。(这里的命令,都可以点鼠标完成,但是建议大家用命令)

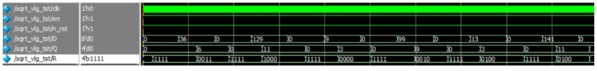

结果出来了,是个非冗余开方,用的是改进的不恢复余数算法。其中,D是被开方数,Q是商,R是余数。

开方的原理跟除法差不多,都是先上商,然后再逼进实际值。

这个算法是向左逼进,如果要算63的开平方,得到的是7,误差有点大。其中,迭代的次数越多,计算的结果越精确(余数的位数越长)。

sqrt(36)=6,结果正确。

sqrt(129)=11,结果正确(取整之后的结果)。

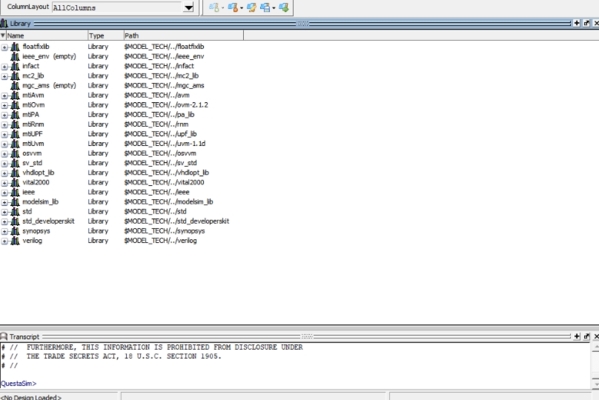

怎么添加库

在软件中想要进行仿真的话,首先需要先在软件中添加库,软件虽然自带了仿真库,但是有些仿真作业还是需要用到某些厂家的FPGA仿真库,如果都在每次仿真过程中进行加载,会花费大量的时间,所以小编为大家带来库的添加方法, 将添加的库设置为默认仿真库,轻松进行仿真。

1、首先确认已经正确安装好QuestaSim和ISE两个软件(本文以QuestaSim10.1和ISE10.1为例)。找到ISE安装目录中../bin/nt文件夹,点击运行其中的compxlib.exe文件。

2、在弹出的对话框中,选择ModelSim(QuestaSim是ModelSim支持SystemVerilog的版本,两者需要的Xilinx库文件完全相同),然后选择QuestaSim位置(QuestaSim位置要指定到win32文件夹位置,所图所示),完成后点击Next。

3、在接下来的对话框中,选择要编译库的语言,可以单独选择VHDL、Verilog以及两者都选择,之后点击Next,选择FPGA器件,可以针对需要选择相应的器件,或者选择全部器件,选择完毕后点击Next。

4、接下来的窗口,需要制定生成库的类型,UNISIM和XilinxCoreLib库一般用来进行功能仿真,SIMPRIM一般用来进行时序仿真,通常都需要选上。选择完毕后点击Next。

5、接着输入生成Xilinx库文件的位置,默认位置是ISE安装目录下。点击Next后,工具会自动生成QuestaSim需要的库文件。

6、待工具生成库文件结束后,在QuestaSim安装目录下,找到modelsim.ini配置文件,将编译好的库文件路径加入到该文件中,这样下次启动时,QuestaSim会自动加载配置的库。

怎么生成波形

在软件中进行仿真的过程中需要进行波形的生成,很多的用户不知道波形生成的方法,其中波形分为DUT波形和TB波形,下面小编为大家带来波形的生成方法。

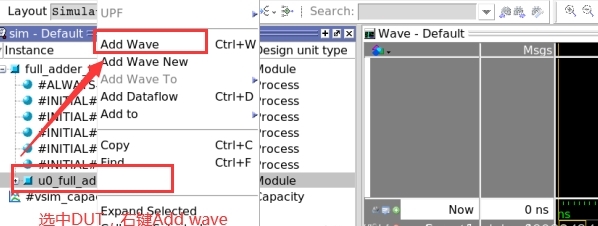

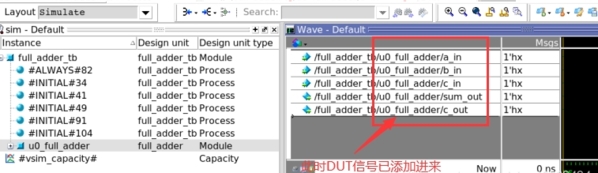

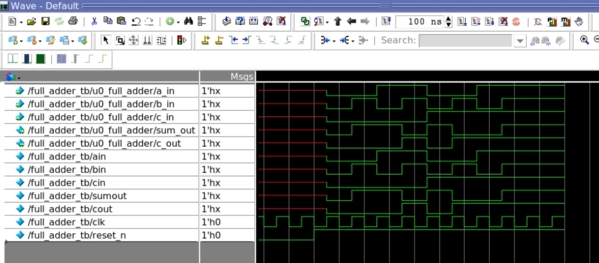

1、首先选中我们的DUT,然后右击选择【add wave】

2、这时我们可以看到DUT已经添加到列表中了

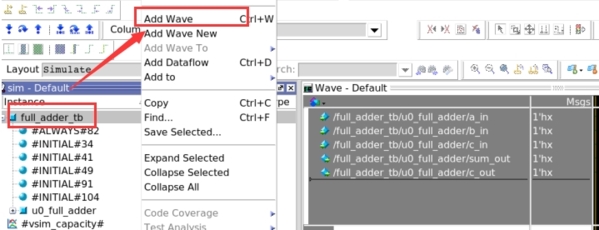

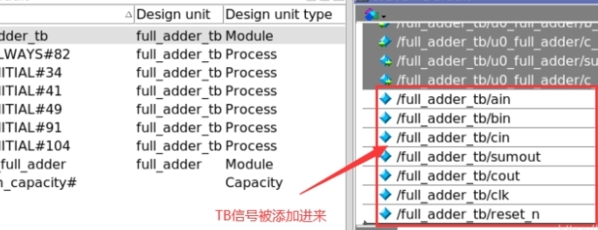

3、接下来同样的步骤,我们将TB信号也添加到列表中

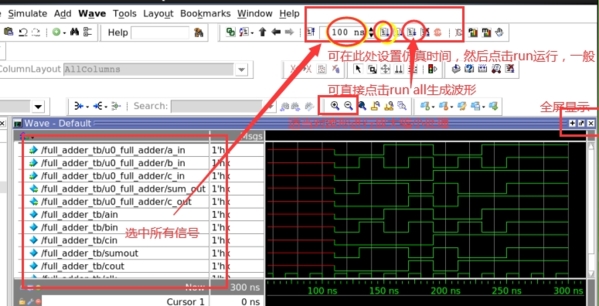

4、所有信号都添加后,可选中所有信号,run all生成波形;波形的结束以代码中的$finish;为仿真结束终点。也手动可设置仿真时间。

全屏显示:

怎么设置波形颜色

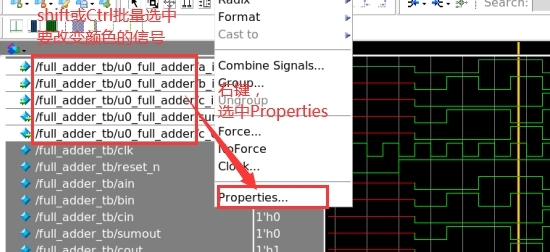

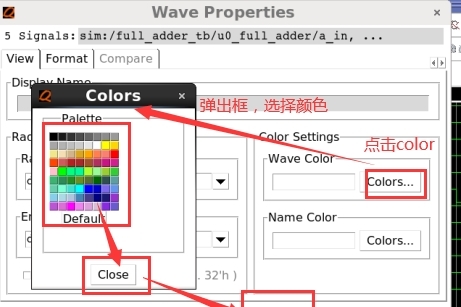

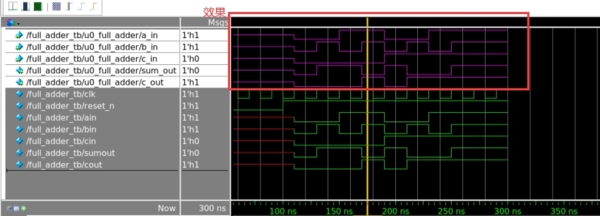

1、选中信号,右键Properties,设置颜色

先点击color后,弹出颜色选择框,

新增功能

1、改进了SystemVerilog性能,语法支持,扩展

2、改进的VHDL性能默认值

3、改进的SystemC 2.3.2支持和默认

4、Visualizer调试高性能和高容量(VIS)

5、覆盖率-自适应排除,多位表达式,FSM,切换改进

6、覆盖范围-现在默认使用10.7x的新报告开关

7、不再支持旧版-novopt选项

8、可视化工具调试高性能和大容量(VIS)

标签: 仿真模拟

装机必备软件

网友评论