Altair PollEx 2021是一个功能强大的PCB设计软件,拥有许多功能,包括查询、测量、查找对象以及各种报告,适用于多种环境下的ECAD和仿真环境。让广大设计人员可以在设计电路板的时候更加的高效,并且可以导出为通用的格式,适用于各类PCB制作的设备。还涵盖设计审查,分析和制造,彻底改善多学科工程师之间的沟通,提升效率,并结合实际情况进行解决方案的定制。本次带来的是最新的中文破解版,安装包中附带了破解补丁,同时还有详细的破解教程,需要的用户不要错过。

软件特色

1、统一零件库

通用的统一零件库支持所有设计过程,使来自不同学科的工程师能够有效地协作进行项目,共享集中在一处的物理,逻辑,热,电气和装配属性数据。

2、原理图设计审查

除行业中性格式外,PollEx还可以从所有主要ECAD供应商(包括Cadence,Mentor Graphics,Zuken和Altium)导入设计。它的建模功能支持设计审查,包括原理图和PCB数据之间的比较,因此可以在过程的早期发现并解决故障,而无需昂贵的ECAD许可证。

3、PCB审查,检查和验证

Pollex具有无与伦比的读取主要ECAD文件格式的功能和易于使用的应用程序,可促进从事原理图和PCB设计的专家团队的协作。改善电路板布局,并使用仿真工具来驱动设计,以实现信号完整性,电源完整性,EMI漏洞和ESD保护。

在BOM,逻辑和PCB级别上跟踪并通知多学科团队成员设计变更和修订,导出验证结果的智能文档报告,并轻松共享设计更新文档以始终保持最高的设计质量。

4、PCB分析与优化

除了内置的分析功能外,PollEx还可以导出到其他Altair和第三方物理模拟工具。您可以利用Altair单元来利用我们的求解器来自信地识别和纠正开发早期的设计问题。使用Altair ElectroFlo™进行不需要高级CFD知识的早期热分析。使用Altair SimLab™通过强大且可重复的工作流程自动执行结构应力,振动和跌落测试性能,从而获得快速,准确和一致的结果。使用Altair Feko™进行详细的EMI / EMC分析。

5、制造设计

通过将制造,安装,镶板和测试数据导出到生产线机械来提高PCB生产效率。超过500种可制造性(DFM)设计检查涵盖了板,组件,钻头,FPCB,封装,焊盘,图案,放置和工具的制造领域。自动化和可定制的测试可以更早地发现潜在的可制造性问题并提高良率。

6、组装和测试设计

提供了一套用于设计PCB的工具,同时考虑了易于组装和线下测试的问题。避免了超过50种的装配设计(DFA)检查是否存在与碰撞,引线,放置,组件和电路板有关的装配问题。 通过将制造,安装,镶板和测试数据导出到生产线机器,提高了PCB制造,组装和线下测试的效率。

安装方法

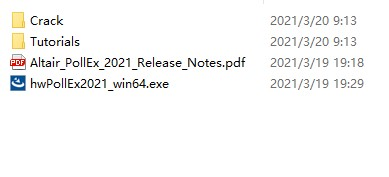

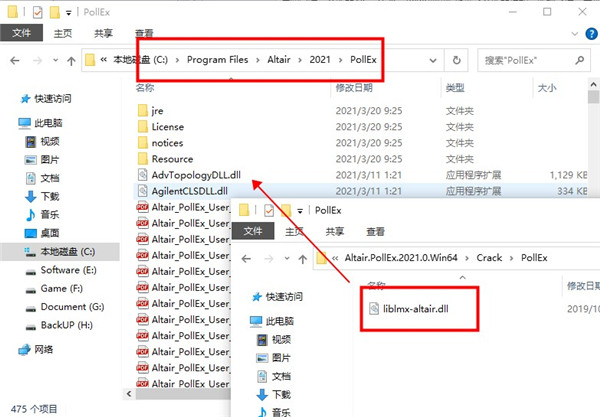

1、在本站下载并解压,得到如下文件

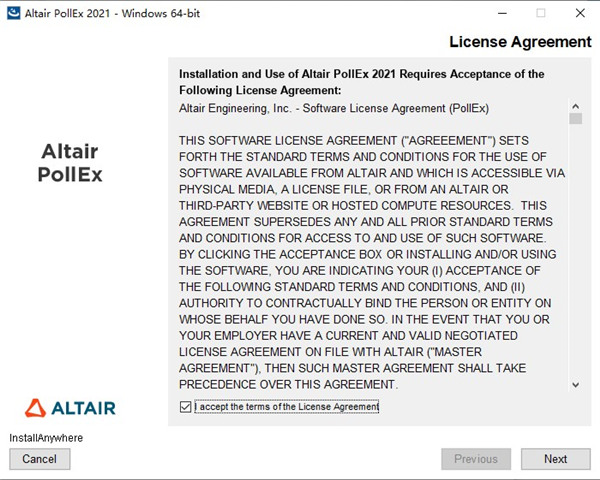

2、双击运行hwPollEx2021_win64.exe,安装原程序,进入安装向导,勾选我同意许可协议,点击Next

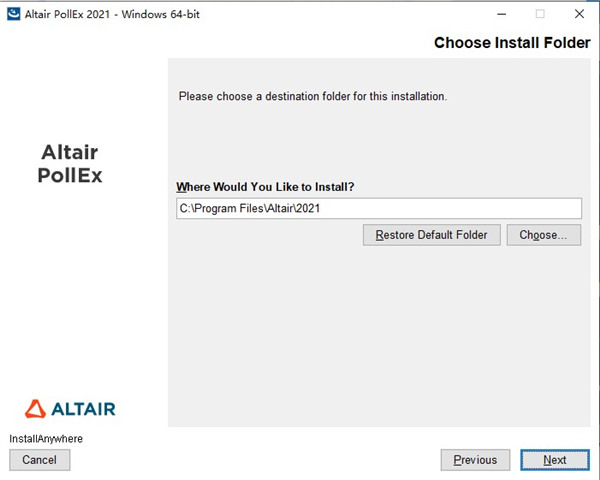

3、选择软件安装路径,默认即可

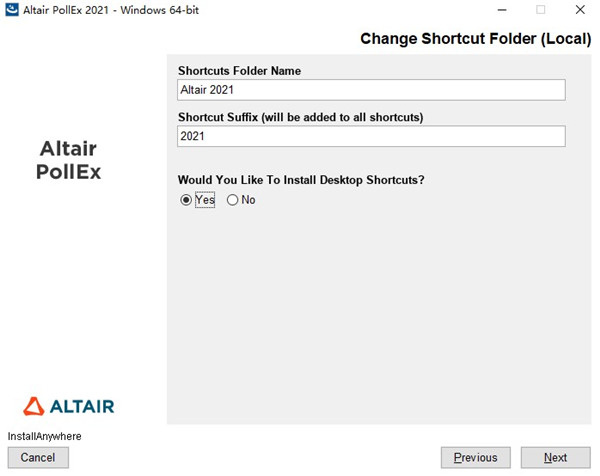

4、选择创建快捷方式,方便之后运行

5、等待安装完成,点击done退出引导

6、将破解补丁复制到软件根目录下,如图所示;

默认路径:C:\Program Files\Altair\2021\PollEx

7、软件破解完成,桌面运行软件,所有功能均可免费无限制使用

新功能

1、添加功能以导出图层图像

支持导出图稿层和物理层的图像。支持的格式为“ JPG和.BMP格式。可以从PollEx PCB中的文件-导出至-图像菜单中使用此功能。

2、添加功能以支持LPDDR4分析

用于分析LPDDR4的功能,该功能已添加到PollEx SI的自动DDR总线分析功能中。 LPDDR4时序标准表已添加。

在现有的DDR技术中。 Vref yoltage,它是定时数据和地址总线的测量参考。用作固定值,但LPDDR4中的Vref电压是通过训练过程在IC内部生成的。如果使用了使用分析结果提取Vref DQ选项,则以JEDEC指定的方式搜索Vref值。作为对所有IC的数据/地址总线的分析结果,可获得最张开眼睛的电压电平。 Vref值由它们的中间值确定。如果使用了“使用用户定义的值”选项,则用户可以设置所需的Vref值。

3、将Sl替换为HyperSpice引擎

PollEx SI的Spice引擎已从Polliwog Spice更改为HyperSPICE,因为只有Spice引擎在同一用户GUI的内部进行了更改。但是,默认的Spice Control参数已更改

4、添加阻抗图的特征

添加了在PollEx DFE +的阻抗检查项目的结果中显示阻抗图的功能。 在结果表中单击“阻抗图”按钮后执行阻抗检查后,将显示“阻抗图”对话框。 通过使用此菜单,用户可以轻松找到整个BUS整个路径中的阻抗失配区域。

5、添加串扰耦合表映射功能

添加了在PollEx DFE +的“串扰噪声”检查项目的结果中显示“后向串扰系数(kb)”耦合图的功能。 在结果表中单击“耦合图”按钮后执行“串扰噪声”检查后,将显示“耦合图”对话框。 通过使用此菜单,用户可以轻松找到整个BUS整个路径中串扰容易受到影响的区域。

6、添加电源完整性检查功能

PollEx DFE +中增加了检查功率饱和度的功能。 新添加的功能是IR下降,环路电感和PDN阻抗

IR-Drop Check:IR下降是指出现在电网电阻组件上的电压下降。 IR降是电流流动期间电源与负载组件之间的电位差。 如果提供给普通的电压电平是。

由于IR-Drop而上升。 系统出现故障或唾液的Risina / Fallina时间不正确。 导致信号完整性问题。 因此,为了使组件正常工作,有必要检查IR-Drop的量是否在组件允许的极限值之内。此项检查指定组件的电压电平是否低于指定电平。

回路电感检查:在PCB中。 电源线通常是指连接电源(VRM)和负载组件的电源网络。

这些电源走线配置的特性可以通过PCB的电源传输网络(PDN)来确定,PDN的运行就像无源组件(例如线圈或电容器)一样。 取决于其物理性质。 由于这些鼻孔成分而产生谐振,并且流过谐振结构的电流会引起局部失真和FM问题,通常应将PDN阻抗设计得尽可能低,通常是为了使PDN阻抗低。 在电源引脚周围安装了一个去耦电容器。 为了使该去耦合电容器有效工作,必须将电源引脚和去耦电容器之间的环路电感设计为较小。此项检查电源引脚和去耦合电容器之间的倾斜电感是否超过用户指定的值。

PDN阻抗检查:在PCB中,电源线通常是指连接电源(VRM)和负载组件的电源网络。

这些电源走线配置的特性可以通过PCB的电源传输网络(PDN)来确定。 根据其物理特性,PDN的工作方式类似于无源组件,例如线圈或电容器。 由于这些无源元件而产生谐振,并且流过谐振结构的电流会引起弦失真和EMI问题。 因此,在设计阶段对PDN阻抗的精确分析非常重要。

此项检查指定电源引脚的PDN阻抗是否高于用户指定的目标阻抗。

7、添加功能以导出热结果

在PollEx Thermal中,添加了以标准文件格式输出热分析结果的功能。 分析结果可以Excel格式或格式输出。 CSV格式。 在“热分析”对话框中,使用“文件/导出到CSV”菜单,用户可以生成结果文件。 分析结果之中。 PCB顶部/底部表面温度将保存为desianname顶部/底部。 xlsx文件,保存的格式是X Y坐标和温度值。 组分温度另存为设计名称Component。 xlsx文件,保存的格式是“参考名称”。 PlaceLaver.XY坐标和温度值。

精品推荐

-

Altium Designer10破解工具

详情 -

MasterCAM X9注册机

详情 -

Altium Designer绿色版

详情 -

MasterCAM9.1汉化版

详情 -

Master Cam 2020

详情 -

Master Cam 2017完整汉化包

详情 -

Multisim14元件库大全

详情 -

Proteus仿真软件

详情 -

奎享雕刻

详情 -

机械工程师CAD2020企业版破解

详情 -

迈迪三维设计工具集6.0注册码破解版

详情 -

FastCAM套料软件

详情 -

WECON LEVI Studio

详情 -

Protel99SE全中文版支持win10

详情 -

Master Cam 2017

详情 -

浩辰CAD机械2022永久激活版

详情

装机必备软件

网友评论